## Temperature dependent properties of InSb and InAs nanowire field-effect transistors

Henrik A. Nilsson,<sup>1,a)</sup> Philippe Caroff,<sup>1</sup> Claes Thelander,<sup>1</sup> Erik Lind,<sup>1</sup> Olov Karlström,<sup>2</sup> and Lars-Erik Wernersson<sup>1</sup>

<sup>1</sup>Division of Solid State Physics, Lund University, Box 118, S-22100 Lund, Sweden <sup>2</sup>Division of Mathematical Physics, Lund University, Box 118, S-22100 Lund, Sweden

(Received 7 October 2009; accepted 26 March 2010; published online 16 April 2010)

We present temperature dependent electrical measurements on InSb and InAs nanowire field-effect transistors (FETs). The FETs are fabricated from InAs/InSb heterostructure nanowires, where one complete transistor is defined within each of the two segments. Both the InSb and the InAs FETs are n-type with good current saturation and low voltage operation. The off-current for the InSb FET shows a strong temperature dependence, which we attribute to a barrier lowering due to an increased band-to-band tunneling in the drain part of the channel. © 2010 American Institute of Physics. [doi:10.1063/1.3402760]

During the past years, much attention has been drawn to nanowire wrap-gate field-effect transistors (FETs) due to the excellent control of the channel electrostatics and good scaling properties.<sup>1,2</sup> Moreover, the possibility to use the nanowire technology to integrate a channel of high electron mobility semiconductor in a cheap silicon process has stimulated research.<sup>3</sup> In the nanowire geometry, several channel materials have been investigated, such as InAs, Si, Si/Ge, and ZnO.<sup>4-7</sup> Recent advances in nanowire epitaxy now also enabled the growth of high crystal quality InSb<sup>8-10</sup> and InAs/InSb heterostructure nanowires,<sup>11</sup> which are potential candidates for FETs.<sup>12</sup> This material has shown good low-temperature magnetotransport properties with large g-factors.<sup>13</sup> Here, we explore the use of InSb nanowires as nanowire FETs and in particular we study the temperature dependence of the transport. As a reference we investigate InAs nanowire transistors processed simultaneously within the same nanowires, since InAs is presently the most investigated III-V semiconductor material for nanowire FETs.

The InAs/InSb heterostructure nanowires were grown in a standard metalorganic vapor phase epitaxy reactor at a pressure of 10 kPa. The substrate temperature was set at 450 °C and the InAs nanowire segment was grown for 7 min. using trimethylindium (TMIn) and arsine (AsH<sub>3</sub>), with molar fractions, respectively, of  $4.6 \times 10^{-6}$  and  $3.8 \times 10^{-4}$ . Then AsH<sub>3</sub> was switched off and trimethylantimony (TMSb) was switched on immediately with a molar fraction of 8.6  $\times 10^{-5}$  to grow the InSb segment for 20 min. The diameters for InAs and InSb segments were  $44 \pm 4$  nm and  $77 \pm 4$  nm, respectively, and the length could vary considerably depending on position on the substrate (about 700 nm for InAs and 1  $\mu$ m for InSb). These nanowires have no measurable tapering or lateral growth for neither InAs nor InSb. The interface between InAs and InSb was shown previously to be nearly atomically abrupt<sup>11</sup> and strain is elastically relaxed within a few nanometers from the interface surface.<sup>14</sup> The InAs segment is quite pure wurtzite with few stacking faults, and InSb is stacking fault-free zinc blende, and could contain between 1% and 4% or As.<sup>14,15</sup> During growth of the InSb segments, some arsenic from the InAs segment evaporates

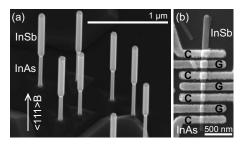

due to the lack of As overpressure, but postgrowth high resolution transmission electron microscope (TEM) analysis, in combination with point analysis and line analysis using x-ray energy dispersive spectroscopy prove that the InAs bottom segment remain a pure binary (no antimony enrichment as a shell or InAsSb alloy formation).<sup>15</sup> No intentional doping was used but carbon may be incorporated from the metalorganic precursor at the low temperature used.<sup>16,17</sup> Typical wires after growth are shown in Fig. 1(a).

Two top-gated transistors were fabricated on each wire, one on the InSb segment and one on the InAs segment. The grown InAs/InSb heterostructure nanowires were transferred from the growth substrate to degenerately doped Si substrates with a 100-nm-thick SiO<sub>2</sub> capping layer. Four 140nm-wide Ti/Au contacts with a spacing of 250 nm were defined to each nanowire by electron beam lithography such that two contacts are placed on each side of the heterostructure interface. Prior to contact metal deposition, the exposed semiconductor contact areas were briefly etched in a  $(NH_4)_2S_x$  solution followed by a rinse in H<sub>2</sub>O. A 10-nmthick dielectric was deposited using atomic layer deposition (ALD), at a temperature of 100 °C, in a  $3 \times 3 \ \mu m^2$  square on each wire, also covering the metal contacts. Two samples were fabricated, one using Al<sub>2</sub>O<sub>3</sub> and one using HfO<sub>2</sub>. Finally, 140-nm-wide Ti/Au finger gates were defined on each center part of the two transistors, such that the gate-contact

FIG. 1. (a) Scanning electron microscope (SEM) image of InAs/InSb heterostructure nanowires grown on an InAs(111)B substrate using aerosol gold particles with a diameter of 40 nm as initial seeds. The image is recorded with a  $30^{\circ}$  tilt of the substrate from the horizontal direction and the scale bar is uncompensated for the tilt. (b) SEM image of an InAs/InSb heterostructure nanowire, with one FET fabricated on each segment.

150.203.178.63 On: Thu, 10 Jul 2014 04:18:07

<sup>&</sup>lt;sup>a)</sup>Electronic mail: henrik.nilsson@ftf.lth.se.

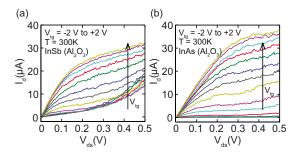

FIG. 2. (Color online) Output characteristics (I-V) of the two materials at RT, (a) InSb and (b) InAs.  $V_{tg}$ =-2 to +2 V (step +0.33 V) for Al<sub>2</sub>O<sub>3</sub> gate dielectric.

spacing was approximately 55 nm on each side of the gate finger. In order to remove the influence of the gate-voltage on the Ohmic contacts, the gates are defined without overlap. However, this also introduces a series resistance where the source and drain extensions remain un-gated. The Ti/Au contact and gate metals were deposited using physical vapor deposition, which produce omeg-alike coverage. A transistor after fabrication is shown in Fig. 1(b).

The output characteristics (I-V) of the InSb and InAs transistors with Al<sub>2</sub>O<sub>3</sub> gate dielectric at room temperature (RT), is shown in Figs. 2(a) and 2(b), respectively. During all measurements the Si substrate is kept at a fixed potential,  $V_{\rm hg}=0$  V. Both transistors show n-type conduction. The overall current level is slightly lower in the InSb transistor; however, the channel conductance,  $g_D = dI_{ds}/dV_{ds}$  for small source-drain voltage,  $V_{ds}$ , and large top-gate voltage,  $V_{tg}$ , is higher. Both transistors show good current saturation and low voltage operation, although the InSb transistor saturates already around  $V_{ds}$ =100 mV, whereas the InAs transistor saturates around  $V_{ds}$ =200 mV. Due to the narrower band gap of InSb, the current below threshold is high as compared to the InAs reference device. We also note that, for negative  $V_{\rm tg}$ , the current increases dramatically as  $V_{\rm ds}$  is raised above about 300 mV, this is due to direct tunneling or impact ionization also originating from the narrow band gap of InSb.

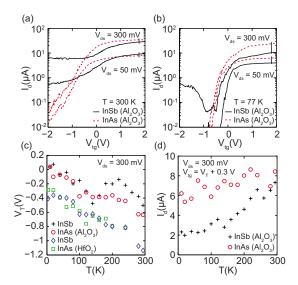

Figures 3(a) and 3(b) displays the transfer characteristics at RT and at 77 K retrieved at  $V_{ds}$ =50 mV and  $V_{ds}$ =300 mV (Al<sub>2</sub>O<sub>3</sub> dielectric). At RT the InSb (solid black curves) off-current saturates with negative  $V_{tg}$  at a large current-level around two orders of magnitude higher than the minimum observed (dashed red curves) off-current for InAs. As the temperature is lowered to 77 K the behavior of the InSb resembles more that of InAs. The InSb transistor shows ambipolar behavior for  $V_{ds}$ =300 mV. This is not observed at  $V_{ds}$ =50 mV, since it requires a  $V_{ds}$  large enough to allow band-to-band tunneling in the gate-drain region.

From the transfer characteristics, it is also possible to deduce the threshold voltage  $(V_T)$ , which is shown in Fig. 3(c). This is done for temperatures in the range between RT and 4.2 K, for both Al<sub>2</sub>O<sub>3</sub> (+,°) and HfO<sub>2</sub> ( $\diamond$ ,  $\Box$ ) gate dielectrics. All threshold voltages are deduced from a linear extrapolation in the transfer characteristics from the point of maximum transconductance  $(g_m)$ . All devices show a similar shift in  $V_T$  toward higher  $V_{tg}$  as the temperature is decreased, however, for Al<sub>2</sub>O<sub>3</sub> a plateau appears between T=100 K and T=200 K. A clear shift in  $V_T$  can also be observed when the dielectric is changed. The dielectric with the lowest permit-This a tivity (Al<sub>2</sub>O<sub>3</sub>) has a more positive threshold voltage, indicat-

FIG. 3. (Color online) (a) Transfer characteristics at RT,  $V_{ds}$ =50 mV and 300 mV. InSb (black solid curve) and InAs (red dashed curve). (b) Transfer characteristics at 77 K,  $V_{ds}$ =50 mV and 300 mV. InSb (black solid curve) and InAs (red dashed curve). (c) Temperature dependence of the threshold voltage,  $V_T$ , in the range between RT and 4.2 K, for both Al<sub>2</sub>O<sub>3</sub> (+, °) and HfO<sub>2</sub> ( $\diamond$ ,  $\Box$ ) gate dielectrics.  $V_{ds}$ =300 mV. (d) Temperature dependence of the conductance at  $V_g$ = $V_T$ +0.3 V. InSb (+) and InAs (°), for Al<sub>2</sub>O<sub>3</sub> gate dielectric.

ing a strong influence of the high-k material and its interface properties. It is further interesting to note that the threshold voltage has similar temperature dependence for the two gate dielectrics even though the channel material varies. All  $V_{tg}$ sweeps shown are recorded at a sweep direction from negative to positive voltage. As the sweep direction is reversed we observe hysteresis in  $I_{ds}$ , although of similar magnitude for the two channel materials.

Comparing the I-V characteristics for the InSb and the InAs segments we find a lower drive current for the InSb, for  $Al_2O_3$  as well as HfO<sub>2</sub> dielectric, even though the diameter is larger and the threshold voltage is similar. Moreover, the InSb nanowire FET shows a larger decrease in drive current and transconductance at reduced temperatures (corrected for  $V_{\rm T}$  shift) as compared to InAs, Fig. 3(d). This is partially related to a larger increase in source/drain resistance,  $1/g_{\rm D}$ , as the temperature is reduced from RT to 77 K (6.1 to 11 k $\Omega$ for InSb and 6.9 to 8.5 k $\Omega$  for InAs). However, the increase in InSb series resistance is too low to account for the reduction in transconductance and drive current. Instead, the reduced current level may be attributed to traps at the InSb high-k interface and increased impurity scattering. Possibly the InSb/high-k interface is less perfect than the InAs/high-k interface since there are less structural defects in the InSb and good transport properties of the InSb nanowires have been verified by low-temperature measurements.<sup>13</sup>

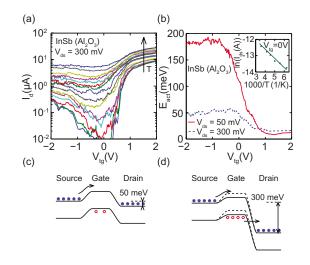

Figure 4(a) shows the transfer characteristics at  $V_{ds}$ =300 mV of the InSb (Al<sub>2</sub>O<sub>3</sub>) segment at temperatures ranging from RT to 4.2 K. At each  $V_{tg}$  an activation energy,  $E_{act}$ , is derived from Arrhenius plots for  $V_{ds}$ =300 mV and  $V_{ds}$ =50 mV. The result is displayed in Fig. 4(b). The typical quality of the  $E_{act}$  fit is displayed as an inset in Fig. 4(b), here for  $V_{ds}$ =300 mV and  $V_{tg}$ =0 V. For  $V_{ds}$ =50 mV,  $E_{act}$  approaches the band gap of InSb,  $E_g$ =170 meV, as  $V_{tg}$  is changed to more negative values. The saturation can thus be such explained by strong inversion under the gate that further to P

FIG. 4. (Color online) (a) Transfer characteristics of the InSb segment at temperatures ranging from RT to 4.2 K, at  $V_{ds}$ =300 mV for Al<sub>2</sub>O<sub>3</sub> gate dielectric. (b) Activation energy,  $E_{act}$ , as a function of  $V_{tg}$ , for  $V_{ds}$ =50 mV (red solid curve) and 300 mV (blue dashed curve). The typical quality of the  $E_{act}$  fit is displayed as an inset, here for  $V_{ds}$ =300 mV and  $V_{tg}$ =0 V. (c) Band diagram, illustrating screening of the gate potential due to inversion under the gate. (d) Band diagram, illustrating increased screening of the gate potential due to an increased band-to-band tunneling current from the valence band in the gate region to the conduction band in the drain region.

screens the gate potential and hence the measured electron current cannot be reduced further, as illustrated in Fig. 4(c). As  $V_{ds}$  is increased to 300 mV,  $E_{act}$  saturates at a much lower value,  $E_{act}$ =50 mV. This can be explained by an increased band-to-band tunneling current from the valence band in the gate region to the conduction band in the drain region, which increases the accumulation of holes under the gate and thus increases the potential underneath the gate,<sup>18</sup> as illustrated in Fig. 4(d). This assignment is supported by the deduction in  $V_{\rm T}$  at the two bias conditions ( $V_{\rm T}$ =-0.44 V at  $V_{\rm ds}$ =50 mV and  $V_{\rm T}$ =-0.50 V at  $V_{\rm ds}$ =300 mV) and a calculation of the characteristic length for a gate-all-around (GAA) structure using,<sup>19</sup>

$$\lambda = \sqrt{\frac{2\varepsilon_{\text{wire}}t_{\text{wire}}^2 \ln\left(1 + \frac{2t_{\text{ox}}}{t_{\text{wire}}}\right) + \varepsilon_{\text{ox}}t_{\text{wire}}^2}{16\varepsilon_{\text{ox}}}},$$

where  $t_{\rm wire}$  is the wire diameter and  $t_{\rm ox}$  is the gate oxide thickness. This gives a characteristic length  $\lambda_{\rm InSb}=27$  nm for the InSb segment,  $t_{\rm InSb}=77$  nm, and  $\lambda_{\rm InAs}=16$  nm for the InAs segment,  $t_{\rm InAs}=44$  nm. The thickness of the Al<sub>2</sub>O<sub>3</sub> gate dielectric is  $t_{\rm ox}=10$  nm, with an estimated dielectric constant of  $\varepsilon_{\rm ox}=9$ . From the characteristic lengths we can deduce that both transistors, in a GAA geometry, are well within the long channel regime,  $L_g > 4.6\lambda$ . While our omega-gated transistors have a slightly larger value of  $\lambda$  as compared with GAA, the used gate length of 140 nm still should be sufficiently long and the reduction in  $E_{\rm act}$  should not be related to drain induced barrier lowering. These facts show that the observed phenomenon may not be attributed to short-channel effects. This is also supported by the InAs reference segments, where we deduced a value well above 300 meV both at  $V_{ds}$ = 50 mV and at  $V_{ds}$ = 300 mV. This is not surprising as the band gap is larger and hence the influence of the dynamic processes across the band gap is weaker.

Scaling of the nanowire diameter will increase the capacitance as well as the transconductance and the band gap<sup>12</sup> and improved doping control will reduce the negative effect of series resistance. These changes are expected to improve the device performance of the FETs toward the full potential of the InSb material system.

In conclusion, we have investigated the properties of InSb nanowire FETs and compared it to InAs nanowire FETs fabricated within the same wire. Both the InSb and the InAs FETs are n-type with good current saturation and low voltage operation.

This work was carried out within the Nanometer Structure Consortium at Lund University and was supported by the Swedish Research Council (VR), the Swedish Foundation for Strategic Research (SSF), the European Community (EU Contract No. 015783 NODE), and the Knut and Alice Wallenberg Foundation.

- <sup>1</sup>J. Feng, G. Thareja, M. Kobayashi, S. Chen, A. Poon, Y. Bai, P. B. Griffin, S. S. Wong, Y. Nishi, and J. D. Plummer, IEEE Electron Device Lett. **29**, 805 (2008).

- <sup>2</sup>T. Bryllert, L.-E. Wernersson, T. Löwgren, and L. Samuelson, Nanotechnology 17, S227 (2006).

- <sup>3</sup>C. Rehnstedt, T. Mårtensson, C. Thelander, L. Samuelson, and L.-E. Wernersson, IEEE Trans. Electron Devices **55**, 3037 (2008).

- <sup>4</sup>C. Thelander, M. T. Bjork, M. W. Larsson, A. E. Hansen, L. R. Wallenberg, and L. Samuelson, Solid State Commun. **131**, 573 (2004).

- <sup>5</sup>C. Yi, D. Xiangfeng, H. Jiangtao, and C. M. Lieber, J. Phys. Chem. B **104**, 9468 (2000).

- <sup>6</sup>L. J. Lauhon, M. S. Gudlksen, D. Wang, and C. M. Lieber, Nature (London) **420**, 57 (2002).

- <sup>7</sup>H. Kind, H. Yan, B. Messer, M. Law, and P. Yang, Adv. Mater. (Weinheim, Ger.) **14**, 158 (2002).

- <sup>8</sup>M. I. Khan, W. Xu, J. Xiaoye, K. N. Bozhilov, and C. S. Ozkan, J. Nanosci. Nanotechnol. 9, 2639 (2009).

- <sup>9</sup>J. H. Seol, A. L. Moore, S. K. Saha, Z. Feng, S. Li, Q. L. Ye, R. Scheffler, N. Mingo, and T. Yamada, J. Appl. Phys. **101**, 023706 (2007).

- <sup>10</sup>D. Canderbat, Y. Zhao, C. Sandow, B. Koshel, C. Yang, and J. Appenzeller, Proceedings of 67th Device Res. Conf., 2009, Vol. 13.

- <sup>11</sup>P. Caroff, J. B. Wagner, K. A. Dick, H. A. Nilsson, M. Jeppsson, K. Deppert, L. Samuelson, L. R. Wallenberg, and L.-E. Wernersson, Small 4, 878 (2008).

- <sup>12</sup>M. A. Khayer and R. K. Lake, IEEE Trans. Electron Devices 55, 2939 (2008).

- <sup>13</sup>H. A. Nilsson, P. Caroff, C. Thelander, M. Larsson, J. B. Wagner, L.-E. Wernersson, L. Samuelson, and H. Q. Xu, Nano Lett. 9, 3151 (2009).

- <sup>14</sup>D. Ercolani, F. Rossi, A. Li, S. Roddaro, V. Grillo, G. Salviati, F. Beltram, and L. Sorba, Nanotechnology **20**, 505605 (2009).

- <sup>15</sup>P. Caroff, M. E. Messing, B. M. Borg, K. A. Dick, K. Deppert, and L.-E. Wernersson, Nanotechnology **20**, 495606 (2009).

- <sup>16</sup>Z. M. Fang, K. Y. Ma, R. M. Cohen, and G. B. Stringfellow, Appl. Phys. Lett. **59**, 1446 (1991).

- <sup>17</sup>E. Lind, A. I. Persson, L. Samuelson, and L.-E. Wernersson, Nano Lett. 6, 1842 (2006).

- <sup>18</sup>B. Brar and H. Kroemer, IEEE Electron Device Lett. 16, 548 (1995).

- <sup>19</sup>C. P. Auth and J. D. Plummer, IEEE Electron Device Lett. 18, 74 (1997).